**ARENBERG DOCTORAL SCHOOL** Faculty of Engineering Science

# Shining Light on Critical Gaps in Memory-Safety:

From Programming Language to Hardware

#### Merve Gülmez

Supervisors:

Prof. dr. ir. W. Joosen

Prof. dr. J.T. Mühlberg

(Université Libre de Bruxelles)

Dr. ir. C. Baumann

(Ericsson AB)

Dissertation presented in partial fulfillment of the requirements for the degree of Doctor of Engineering Science (PhD): Computer Science

December 2025

# SHINING LIGHT ON CRITICAL GAPS IN MEMORY-SAFETY:

#### FROM PROGRAMMING LANGUAGE TO HARDWARE

Merve GÜI MF7

Supervisors:

Prof. dr. ir. W. Joosen Prof. dr. J.T. Mühlberg (Université Libre de Bruxelles) Dr. ir. C. Baumann (Ericsson AB)

Members of the

Examination Committee:

Prof. dr. ir. J. De Schutter, chair

Dr. E. Truyen

Prof. dr. ir. S. Volckaert

Prof. dr. P. Valcke

Prof. dr. ir. F. Piessens

(KU Leuven)

Prof. dr. A. Paolillo

(Vrije Universiteit Brussel)

Dissertation presented in partial fulfillment of the requirements for the degree of Doctor of Engineering Science (PhD): Computer Science

© 2025 Merve Gülmez

Uitgegeven in eigen beheer, Merve Gülmez, Leuven (Belgium)

Alle rechten voorbehouden. Niets uit deze uitgave mag worden vermenigvuldigd en/of openbaar gemaakt worden door middel van druk, fotokopie, microfilm, elektronisch of op welke andere wijze ook zonder voorafgaande schriftelijke toestemming van de uitgever.

All rights reserved. No part of the publication may be reproduced in any form by print, photoprint, microfilm, electronic or any other means without written permission from the publisher.

## **Preface**

This thesis has been a challenging journey for me, as I started from scratch in computer security. That is why I am grateful to those around me for patiently teaching me: Christoph and JT, for providing a security background and for kick-starting my PhD; Thomas, for introducing me to memory-safety hardening techniques and helping me structure the thesis idea; Håkan and Hossam, for our joint work on hardware security; and Hans from SSG and Adriaan, for contributing to my compiler knowledge.

I would also like to thank: Gianluca, for following my progress on this PhD and for your friendship; the CHERI team, especially Hesham, John, Peter, Robert, and Jessica, for all kinds of technical discussions; Alex, for enabling me to explore a new area; Asokan, for being an example with the effort you put in; Jialun, for nice collaboration and building on top of work this thesis started; Anjo, for your valuable feedback; and my interns Sacha, Hugo and Ruben, for making this journey more enjoyable.

To my thesis committee members, Peggy, Eddy, Antonio, Frank, Wouter, and Stijn: thank you for taking the time to read my thesis and for your constructive feedback.

Thomas, I have really enjoyed pursuing all the papers and ideas together, and I am happy that we still have a lot to do. Thank you for believing in me from the beginning and for being with me throughout this thesis. Your encouragement has made this thesis possible and has made me more confident.

Christoph, you spent so much time being the best company during the lockdown and patiently helping me improve my language skills. Thank you for all your time, for our many discussions, and for supporting me.

JT, thank you for managing my cat photos, for our enjoyable discussions, and for coining a term for my language and understanding it. You always managed to support me, no matter what difficulties I have, and you made this journey more fun.

To the 5GhOSTS team: Eva, Wouter, Eddy, Christoph, JT, and Peggy; thank you for making this project possible. I am also grateful to the European Union for financially supporting this thesis. To my 5GhOSTS buddies, Gerald, Mykta, and Gianluca, thank

i

ii \_\_\_\_\_\_ PREFACE

for the time we spent together.

To my Ericsson colleagues: Ulf, thank you for giving me every opportunity I needed. Mohsin, Vlasios, Erik, Eva, Karl, Göran, Francesca, John, Patrik, Niklas, Kim, Christian, Santeri, İlhan, Sini, and Peter, thank you for always being supportive and for all the fika we had together.

To the Distrinet TEE group: thank you for hosting me during my brief visit. Even though, due to the circumstances, I did not have as much time to spend with you as I would have liked, I am proud of this team and happy to read all your exciting papers.

To my former colleagues from NETAS, especially R&D manager Ersin Öztürk: thank you for believing in me at the beginning of my career and for supporting me throughout my master's degree, which led me to pursue my PhD.

To my bachelor's degree teacher and friends: thanks a lot for supporting us during difficult times at school and in periods of political turmoil that burdened us.

To my friend Prajwol: thank you for supporting me through many challenging times and for standing by me throughout this thesis. You, Vani, and Sarita mean a lot to me; Ahmet, thanks for encouraging me to go abroad and welcoming me to Stockholm five years ago; I hope you are proud that I am now graduating. Fatih, your friendship has always been special to me; thank you for still listening my ideas. Rabia, I have no words to express how much your/your family's support, mean to me. I hope that one day, hand in hand with your brother, we will look at the sky and celebrate justice for all people who are suffering now. Emine, Gülsüm, Daniyal, Aydın, Selin, Zeynep, Tuğçe, Süveyda, Betül, Hasan, Nurefsan, and many others who have touched my life: thank you for all your support, the endless talks, and our board game nights!

Anne, senin dualarının hep yanımda olduğunu hissettim. Çok teşekkür ederim. To my little sister, I am happy for every moment we spend together and for the chance to witness your growth. Thank you for all the figures you drew for PhD journey. To my family-in-law, thank you for your endless support and care. Your kindness and warmth have made me feel truly welcomed and loved.

To my cat, Nisan: you are the best company I can imagine; your connection melts my heart. Thank you for all the cuddles and love you give me every day.

To those who have given me unconditional support: you stayed with me through the most difficult moments of this thesis and celebrated the happiest ones, thanks for taking such good care of me. I am grateful beyond words for having you in my life.

To all those oppressed around the world who have lost their freedom or their lives, who have fled their countries, or who continue to struggle to survive: I wrote this thesis with a heavy heart, thinking of you. This thesis is dedicated to all of you.

Merve

## **Popularized Abstract**

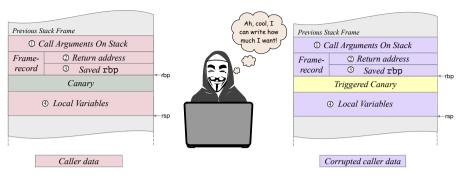

A significant challenge for the development of software that closely interacts with computer hardware is ensuring that every access to computer memory is valid, and that all stored data in memory remains correct. Software that correctly operates on memory is called "memory safe". However, developers might make mistakes during programming that cause software to use memory incorrectly. For example, a program might read or write data outside the memory area that was reserved for it. Such mistakes, called "memory-safety violations", can cause the software application to crash or, in some cases, let hackers break into the computer system. This thesis addresses critical gaps in existing state-of-the-art solutions for memory safety.

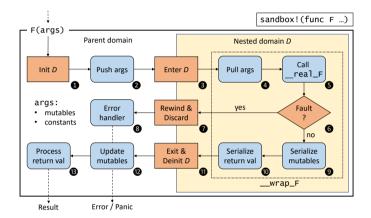

One common practice is to detect memory-safety violations after they occur, for example, with guard variables that check whether memory adjacent to the reserved area has been modified. However, detecting memory-safety violations just makes them less useful for hackers. Only detecting memory-safety violations does not allow the application to continue its job since data might have been (accidentally or intentionally) overwritten and lost, or the wrong data may have made its way throughout the application and corrupted its integrity. To overcome the challenge of detection-based approaches lacking resilience, this thesis proposes *secure rewind and discard*, an approach that allows software to recover from memory-safety violations and continue its job without crashing. The rewind and discard approach requires dividing the program into smaller parts, called *domains*, which limit the effects of memory errors and can be discarded without crashing the application if individual domains are corrupted.

Another approach for preventing memory-safety errors is the use of memory-safe programming languages. These languages make programmers follow stricter rules regarding how memory must be managed, manage memory on their behalf, and automatically add run-time checks to detect memory errors. This thesis examines Rust, a modern language with memory safety. However, Rust code can still call into older, less safe code. We adapt secure rewind and discard to Rust, making it easier for developers to safeguard their Rust applications against errors in such older code.

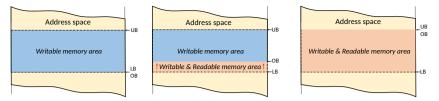

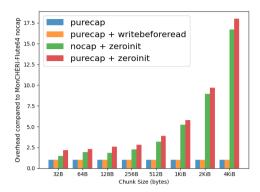

Finally, memory safety can be enforced by computer hardware that validates every memory reference against the memory area that is reserved for that reference. This thesis extends such a hardware architecture, CHERI, which prevents many memory errors but cannot avoid *uninitialized memory* issues, cases where memory content is undefined because the memory is read before being written. We extend CHERI to allow it to track which memory addresses have been written at a particular memory reference, before it allows memory to be read from there.

Through these contributions, this thesis furthers the pursuit of comprehensive memory safety solutions by shining light on previously under-represented challenges: *improving* software resilience and availability, and preventing uninitialized memory access.

# **Gepopulariseerde Samenvatting**

Een belangrijke uitdaging bij de ontwikkeling van software die nauw samenwerkt met computerhardware, is ervoor te zorgen dat elke toegang tot het computergeheugen geldig is en dat alle gegevens die in het geheugen zijn opgeslagen correct blijven. Software die correct werkt met het geheugen wordt "geheugenveilig" genoemd. Ontwikkelaars kunnen echter tijdens het programmeren fouten maken waardoor software het geheugen onjuist gebruikt. Een programma kan bijvoorbeeld gegevens lezen of schrijven buiten het geheugengebied dat ervoor was gereserveerd. Dergelijke fouten, "geheugenveiligheidsinbreuken" genoemd, kunnen ervoor zorgen dat de softwaretoepassing crasht of, in sommige gevallen, dat hackers in het computersysteem kunnen inbreken. Dit proefschrift behandelt gaten in bestaande state-of-the-art oplossingen voor geheugenveiligheid.

Een veelgebruikte methode is om schendingen van de geheugenveiligheid te detecteren nadat ze zich hebben voorgedaan, bijvoorbeeld met beveiligingsvariabelen die controleren of het geheugen naast het gereserveerde gebied is gewijzigd. detecteren van schendingen van de geheugenveiligheid maakt ze echter alleen maar minder bruikbaar voor hackers. Alleen het detecteren van schendingen van de geheugenveiligheid maakt het niet mogelijk dat de applicatie zijn werk voortzet, aangezien gegevens (per ongeluk of opzettelijk) overschreven en verloren kunnen zijn gegaan, of omdat verkeerde gegevens zich door de applicatie kunnen hebben verspreid en de integriteit ervan kunnen hebben aangetast. Om het probleem van detectiegebaseerde benaderingen die niet resiliënt genoeg zijn te overwinnen, stelt dit proefschrift secure rewind and discard voor, een benadering waarmee software kan herstellen van schendingen van de geheugenveiligheid en zijn werk kan voortzetten zonder te crashen. De rewind and discard-benadering vereist dat het programma wordt opgedeeld in kleinere delen, domeinen genaamd, die de effecten van geheugenfouten beperken en kunnen worden verwijderd zonder dat de toepassing crasht als afzonderlijke domeinen beschadigd zijn.

Een andere manier om geheugenveiligheidsfouten te voorkomen, is het gebruik van geheugenveilige programmeertalen. Deze talen zorgen ervoor dat programmeurs strengere regels moeten volgen voor het beheer van het geheugen, beheren het geheugen voor hen en voegen automatisch runtime-controles toe om geheugenfouten op te sporen. Deze scriptie onderzoekt Rust, een moderne taal met geheugenveiligheid. Rust staat ontwikkelaars echter nog steeds toe om oudere onveilige code aan te roepen. We passen secure rewind and discard toe op Rust, waardoor het voor ontwikkelaars gemakkelijker wordt om hun Rust-toepassingen te beveiligen tegen fouten in dergelijke oudere onveilige code.

Ten slotte kan geheugenveiligheid worden afgedwongen door computerhardware die elke geheugenverwijzing valideert ten opzichte van het geheugengebied dat voor die verwijzing is gereserveerd. Dit proefschrift breidt een dergelijke hardwarearchitectuur, CHERI, uit, die veel geheugenfouten voorkomt. CHERI kan echter niet voorkomen dat er gevallen zijn waarin de inhoud van het geheugen ongedefinieerd is omdat het geheugen wordt gelezen voordat het wordt geschreven, ook wel bekend als *niet-geïnitialiseerd geheugen* problemen. We breiden CHERI uit zodat het bijhoudt naar welke geheugenlocaties is geschreven en daarna alleen lezen vanaf die locaties toestaat.

Door middel van deze bijdragen bevordert dit proefschrift het streven naar uitgebreide oplossingen voor geheugenveiligheid door aandacht te besteden aan uitdagingen die tot nu toe onderbelicht zijn gebleven: het verbeteren van de resiliëntie en beschikbaarheid van software en het voorkomen van niet-geïnitialiseerde geheugentoegang.

## **Abstract**

Memory safety refers to a program's property of ensuring that memory is accessed only in valid and intended ways. Memory-safety guarantees can be reinforced through programming languages with built-in safety features, such as garbage collection, compile- and run-time checks, or through hardware-based solutions like capability architectures. This thesis focuses on critical gaps in the current state of the art: the lack of fault tolerance of software-based mitigations for C and C++, limits of the memory-safety properties in Rust, and initialization-time safety in hardware capability architectures, such as CHERI.

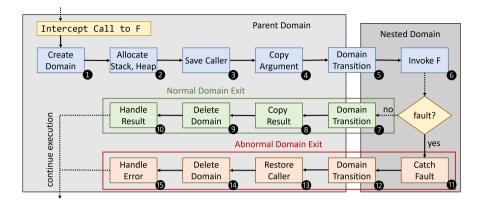

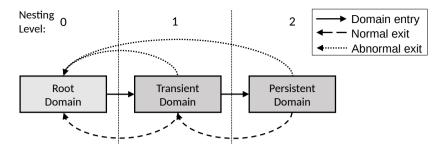

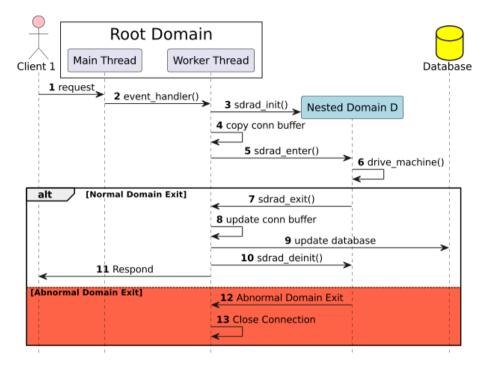

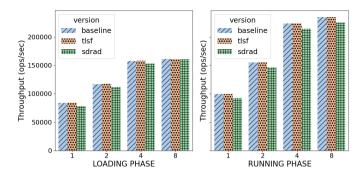

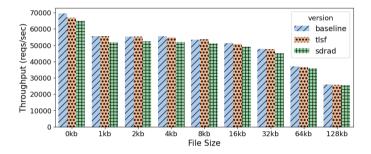

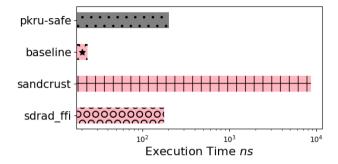

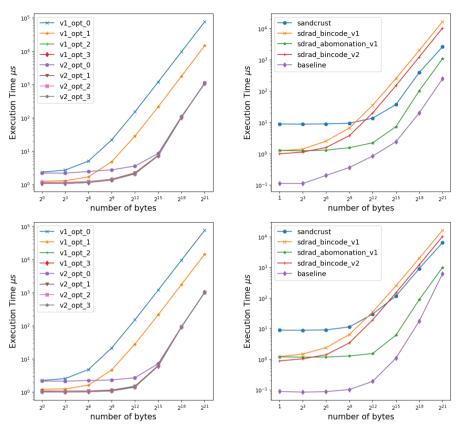

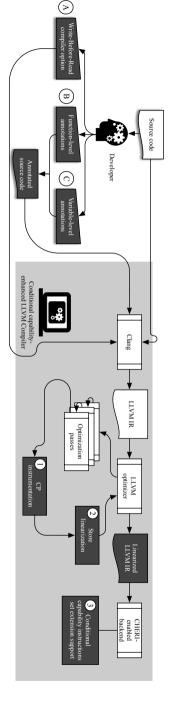

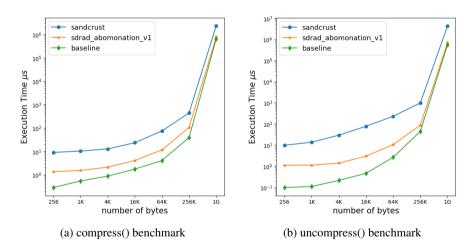

C and C++ are still the preferred languages for system programming, embedded systems, and various critical applications due to their performance. However, these languages lack built-in memory-safety properties. While several well-known defense techniques can mitigate common faults and memory safety vulnerabilities in software, many do not address the challenge of software resilience and availability—specifically, whether a system can continue to function and remain responsive under attack or when subjected to malicious inputs. As a solution, we propose *secure rewind and discard of isolated domains* as an efficient and secure method of improving the resilience of software that is targeted by run-time attacks. We show the practicability of our methodology by realizing a software library for Secure Domain Rewind and Discard (SDRaD) and demonstrate how SDRaD can be applied to real-world software.

Rust has performance characteristics close to traditional system programming languages such as C and C++ but, unlike these languages, Rust has memory safety guarantees enforced by compile-time analysis. However, in order to interact with hardware or call into non-Rust libraries, Rust provides *unsafe* language features that shift responsibility for ensuring memory safety to the developer. Failing to do so may lead to memory-safety violations in Rust code, which can violate the safety of the entire application. To shield safe program sections from safety violations that may happen through unsafe language features, we adapt SDRaD to protect Rust code. To be practical, security features such as SDRaD must be easy for developers to adopt. We design a Rust-native application programming interface for SDRaD that

viii \_\_\_\_\_\_ ABSTRACT

leverages Rust's powerful metaprogramming features to enable easy sandboxing of unsafe interfaces

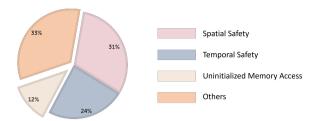

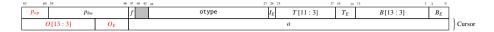

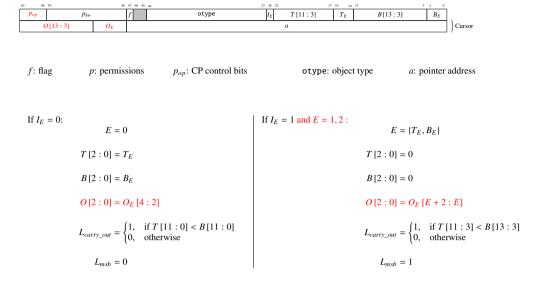

Up to 10% of memory-safety vulnerabilities in languages like C and C++ stem from uninitialized variables. Capability-based addressing, such as CHERI, mitigates many memory defects, including spatial and temporal safety violations at an architectural level. CHERI, however, does not handle undefined behavior from uninitialized variables. We extend the CHERI capability model to include "conditional capabilities", enabling memory-access policies based on prior operations. This allows enforcement of policies that satisfy memory-safety objectives such as "no reads to memory without at least one prior write".

Through these contributions, this thesis furthers the pursuit of comprehensive memory safety solutions by shining light on previously under-represented challenges: *improving* software resilience and availability and preventing uninitialized memory access.

As complementary contributions, this thesis presents an efficient and comprehensive system call interposition mechanism, and provides compiler-assisted automated compartmentalization for Rust. In addition, it evaluates different memory-safety-defense techniques, such as stack canaries and shadow stacks, in terms of their effectiveness and performance. Orthogonally to these works, it proposes an extension to CHERI for enforcing data oblivious computation to harden software against timing side channels. Finally, it discusses environmental sustainability considerations related to SDRaD.

## Beknopte samenvatting

Geheugenveiligheid verwijst naar de eigenschap van een programma dat het alleen op een geldige en beoogde manier omgaat met geheugen. Geheugenveiligheid kan worden versterkt door programmeertalen met ingebouwde veiligheidsfuncties, zoals *garbage collection*, toegangscontroles tijdens het compileren en uitvoeren, of door hardwaregebaseerde oplossingen zoals capability-architecturen. Dit proefschrift richt zich op de hiaten in de huidige stand van zaken: het gebrek aan fouttolerantie van softwaregebaseerde mitigaties voor C en C++, de beperkingen van de geheugenveiligheidseigenschappen in Rust en de initialisatiezekerheid in hardwarecapaciteitsarchitecturen, zoals CHERI.

C en C++ zijn vanwege hun prestaties nog steeds de voorkeurstalen voor systeemprogrammering, *embedded* systemen en diverse kritieke toepassingen. Deze talen

missen echter ingebouwde geheugenveiligheidseigenschappen. Hoewel verschillende

bekende verdedigingstechnieken veelvoorkomende fouten en kwetsbaarheden in de

geheugenveiligheid van software kunnen beperken, bieden veel daarvan geen oplossing

voor de uitdaging van softwareresiliëntie en -beschikbaarheid, met name de vraag

of een systeem kan blijven functioneren en responsief kan blijven bij aanvallen of

wanneer het wordt blootgesteld aan kwaadaardige invoer. Als oplossing stellen we

veilig terugspoelen en verwijderen van geïsoleerde domeinen voor als een efficiënte

en veilige methode om de resiliëntie van software die het doelwit is van runtimeaanvallen te verbeteren. We tonen de bruikbaarheid van onze methodologie aan

door een softwarebibliotheek voor Secure Domain Rewind and Discard (SDRaD)

te construeren en we laten zien hoe SDRaD kan worden toegepast op echte software.

Rust heeft prestatiekenmerken die dicht bij traditionele systeemprogrammeertalen zoals C en C++ liggen, maar in tegenstelling tot deze talen biedt Rust garanties voor geheugenveiligheid die worden afgedwongen door analyse tijdens het compileren. Om echter te kunnen communiceren met hardware of om niet-Rust-bibliotheken aan te roepen, biedt Rust *unsafe* taalfuncties die de verantwoordelijkheid voor het waarborgen van geheugenveiligheid verschuiven naar de ontwikkelaar. Als dit niet gebeurt, kan dit leiden tot schendingen van de geheugenveiligheid in Rust code, wat de

veiligheid van de hele applicatie in gevaar kan brengen. Om veilige programmasecties te beschermen tegen veiligheidsschendingen die kunnen optreden door onveilige taalfuncties, passen we SDRaD aan om Rust code te beschermen. Om praktisch te zijn, moeten beveiligingsfuncties zoals SDRaD gemakkelijk door ontwikkelaars kunnen worden toegepast. We ontwerpen een *Rust-native* applicatie-programmeerinterface voor SDRaD die gebruikmaakt van de krachtige meta-programmeerfuncties van Rust om eenvoudige *sandboxing* van onveilige interfaces mogelijk te maken.

Tot 10% van de kwetsbaarheden op het gebied van geheugenveiligheid in talen als C en C++ zijn het gevolg van niet-geïnitialiseerde variabelen. Geheugenadressering op basis van *capabilities*, zoals CHERI, vermindert veel geheugendefecten, waaronder ruimtelijke en temporele veiligheidsschendingen op architecturaal niveau. CHERI kan echter geen ongedefinieerd gedrag van niet-geïnitialiseerde variabelen afhandelen. We breiden het CHERI *capability*-model uit met "Conditionele *Capabilities*", waardoor geheugentoegangsbeleid op basis van eerdere operaties mogelijk wordt. Hierdoor kan beleid worden afgedwongen dat voldoet aan doelstellingen op het gebied van geheugenveiligheid, zoals "geen leesbewerkingen op deze geheugenlocatie zonder ten minste één voorgaande schrijfbewerking".

Via deze bijdragen bevordert dit proefschrift het streven naar uitgebreide oplossingen voor geheugenveiligheid door licht te werpen op uitdagingen die voorheen onderbelicht bleven: het verbeteren van de resiliëntie en beschikbaarheid van software en het voorkomen van niet-geïnitialiseerde geheugentoegang.

Als aanvullende bijdragen presenteert dit proefschrift een efficiënt en uitgebreid mechanisme voor het onderscheppen van systeemaanroepen en beschrijft het geautomatiseerde, compiler-ondersteunde compartimentalisatie voor Rust programma's. Daarnaast worden verschillende technieken voor geheugenveiligheid, zoals *stack canaries* en *shadow stacks*, geëvalueerd op hun effectiviteit en prestaties. Orthogonaal aan deze werken stelt dit proefschrift een uitbreiding op CHERI voor om *data-oblivious computation* af te dwingen zodat software versterkt wordt tegen timing *side channels*. Ten slotte worden overwegingen met betrekking tot de duurzaamheid van SDRaD besproken.

## **List of Abbreviations**

**%ebp** x86 base pointer register. 5

**%rbp** x86-64 base pointer register. 5, 7

**%rsp** x86 and x86-64 stack pointer register. 5

**ALU** arithmetic logic unit. 22, 93, 94

**API** application programming interface. 11, 15–17, 19, 20, 36, 42, 44, 47, 49, 50, 57, 59, 62, 63, 65–69, 74, 75, 98, 101, 113, 116

**ASLR** address-space layout randomization. 6, 26, 41, 43, 50, 52, 82, 106

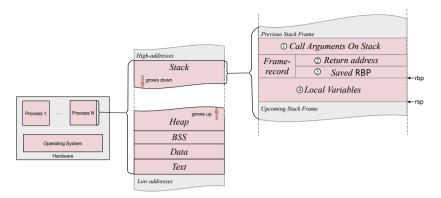

**BSS** block starting symbol. 3

BTB branch-target buffer. 22

**CFI** control-flow integrity. 6, 26, 50

**CHERI** Capability Hardware Enhanced RISC Instructions. viii, xxi, 2, 12–14, 16–18, 21, 22, 50, 81–86, 88, 89, 91, 93–96, 98, 99, 101, 102, 104, 107–111, 114

CISA Cybersecurity & Infrastructure Security Agency. 2, 12

**CoTS** commercial off-the-shelf. 28, 52, 53

**CP** conditional permission. 17, 83, 84, 86, 87, 89–94, 96, 98, 99, 101, 102, 107–110, 134, 135

CVE Common Vulnerability Enumeration. 14, 84

**DoS** denial-of-service. 1, 2, 7, 14, 26

**DPC++** Data Parallel C++. 105

xii \_\_\_\_\_\_ List of Abbreviations

**FFI** foreign function interface. 2, 10, 51, 56, 57, 62, 63, 65, 79

FPGA field-programmable gate array. 18, 82, 99, 102, 108

g.m. geometric mean. 103

GEP GetElementPtr. 97, 98

IP intellectual property. 83, 92, 93, 99

IPC inter-process communication. 60, 66, 115, 116

IR intermediate representation. 96, 97

**ISA** instruction-set architecture. 5, 12, 82, 85, 89, 92, 94, 99, 107

**JIT** just-in-time. 90

LAM Linear Address Masking. 94

LB lower bound. 87

**LUT** lookup table. 99

MMU memory management unit. 3, 52, 85

**MPK** Memory Protection Keys. 15, 16, 19, 20, 29, 55, 57, 115

MSRC Microsoft Security Response Center. xxi, 13, 14, 82, 84, 86

MSVC Microsoft Visual C++. 104–106

NIST National Institute of Standards and Technology. 20, 83, 99

NSA National Security Agency. 2

**OB** operation bound. 87, 89, 90, 92–94, 96, 109

**ONCD** Office of the National Cyber Director. 12

**OS** operating system. 3, 26, 28, 29, 61, 94

PCC program counter capability. 91

**PKRU** protection key rights register. 15, 19, 20, 40–42, 48, 52, 61, 69, 75

**PKU** Protection-Keys for Userspace. 27, 29, 36, 40, 49, 52, 63, 68, 74

LIST OF ABBREVIATIONS \_\_\_\_\_\_\_xiii

RSB return stack buffer. 22

**SFI** sofware-fault isolation. 8, 28, 29, 40, 42, 52, 61

SGX Software Guard Extensions. 34, 50, 51

**SLOC** source lines of code. 10, 45, 48

SSA static single-assignment. 96, 97

STL store to load. 22

SUD syscall user dispatch. 19

TBI Top Byte Ignore. 94

TEE trusted execution environment. 51

**TLSF** Two-Level Segregated Fit. 42, 46, 48, 62, 67, 92, 103

UAI Upper Address Ignore. 94

**UB** upper bound. 87

**x86-64** 64-bit x86. xxi, 3, 5, 15, 20, 21, 27, 115

**XOM** execute-only-memory. 90

# **List of Symbols**

```

a address. 95

```

E exponent. 95

$I_E$  internal exponent. 95

MW mantissa width. 95

b base. 93, 95

o operation top. 93, 95, 109, 110

t top. 95, 109

## **Contents**

| Po | pula   | rized Abstract                                               | iii   |

|----|--------|--------------------------------------------------------------|-------|

| G  | ерори  | ulariseerde Samenvatting                                     | v     |

| ΑI | ostrac | ct                                                           | vii   |

| В  | eknop  | ote samenvatting                                             | ix    |

| Li | st of  | Abbreviations                                                | xiii  |

| Li | st of  | Symbols                                                      | χV    |

| Li | st of  | Symbols                                                      | xvii  |

| Co | onten  | its                                                          | xvii  |

| Li | st of  | Figures                                                      | xxi   |

| Li | st of  | Tables                                                       | xxiii |

| 1  |        | oduction                                                     | 1     |

|    | 1.1    | Memory Safety and Why It Matters                             | 3     |

|    |        | 1.1.1 Problem Statement, Research Objectives, Methodology    | 6     |

|    |        | 1.1.2 Programming language perspective: Rust                 | 9     |

|    |        | 1.1.3 Memory-safety at hardware level: CHERI                 | 12    |

|    | 1.2    | Thesis Contributions                                         | 15    |

|    | 1.3    | Complementary Contributions                                  | 18    |

| 2  |        | vind & Discard: Improving Software Resilience using Isolated |       |

|    |        | nains                                                        | 25    |

|    | 2.1    | Introduction                                                 | 26    |

|    | 22     | Rackground                                                   | 27    |

xviii \_\_\_\_\_\_ CONTENTS

|   |                                  | 2.2.1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 28                                                                                                             |

|---|----------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------|

|   |                                  | 2.2.2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Software Fault Isolation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 28                                                                                                             |

|   |                                  | 2.2.3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 29                                                                                                             |

|   | 2.3                              | Secure                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Domain Rewind and Discard                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 29                                                                                                             |

|   |                                  | 2.3.1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Threat Model and Requirements                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 0                                                                                                              |

|   |                                  | 2.3.2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | High-level Idea                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 1                                                                                                              |

|   |                                  | 2.3.3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Domain Life Cycle                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 1                                                                                                              |

|   |                                  | 2.3.4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Domain Types and Patterns                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 2                                                                                                              |

|   |                                  | 2.3.5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Domain Nesting and Rewinding                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 5                                                                                                              |

|   |                                  | 2.3.6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Multithreading                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 5                                                                                                              |

|   | 2.4                              | Prototy                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 6                                                                                                              |